지난 포스팅에 애더까지 만들고

testbench를 이용하여 시뮬레이션도 돌려보았다.

오늘은 MUX (먹스) 를 만들어보겠다.

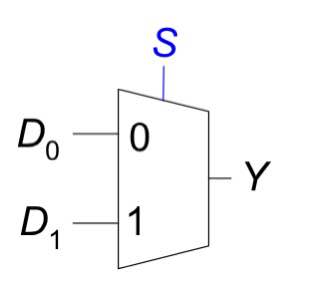

먹스 (MUX) 란 Multiplexer로

출력에 연결하는 N개의 입력 중 하나를 선택하는것이다.

예를 들면 위와 같은 구조에서

S가 0이라면 D0의 값이 Y가 되고

S가 1이라면 D1의 값이 Y가 되는것이다.

그렇다면 이제 verilog를 이용하여 이러한 mux를 어떻게 디자인하냐,,,!

먼저 2:1 mux를 생각해보자

2:1 mux라면 선택지가 d0와 d1 이렇게 두가지만 있는

위의 예시에서 보여준 형태이다.

module 이름을 써주고 입출력을 써준 후

assign으로 할당하여준다.

assign 문에서 ?의 역할이

s에 따라 d1과 d0중 선택하겠다는 뜻이다.

따라서 mux에서는 이렇게 써준다.

여기서 주의할건 뒤에가 0일때라는거임!

그래서 0일 때 d0를 택할거니까 d1:d0로 써줌

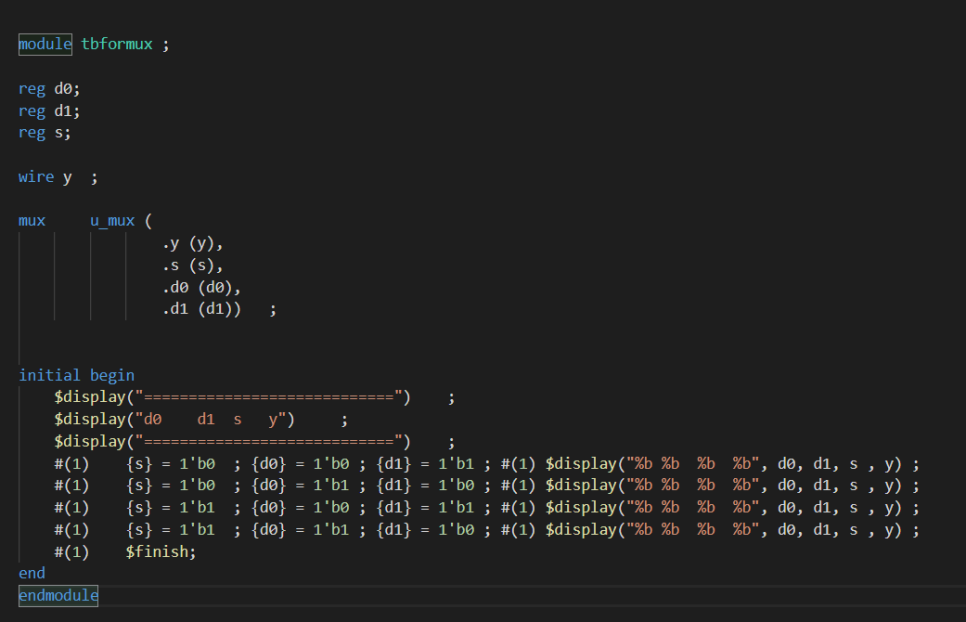

그렇다면 이번에도 마찬가지로 내가 짠 이 mux가 제대로 작동하는지를 확인하기 위해

testbench를 간단히 짜서 확인해보자

간단히 module 이름은 tbformux로 하고

입력은 reg 출력은 wire 선언을 해준다.

그리고 우리가 확인해볼 mux를 써서 불러와주고

각각의 입출력 옆에 들어갈 값들을 써준다.

그리고 display를 이용하여 화면에 나타나는걸 적어준다.

s가 0과 1에 따라 달라지므로 0을 넣었을때와 1을 넣었을때를 보여주기 위해

0과 1을 넣어주고

그에 따라 d0와 d1이 나오는걸 보여주기 위해

d0와 d1에도 다른 입력값을 넣어준다.

그리고 시뮬을 돌려보면

s의 값이

0일때는 d0 의 값이 y로 나오고

1일때는 d1의 값이 y로 나오는 것을 확인할 수 있다.

'디지털 논리 회로 > Verilog (베릴로그)' 카테고리의 다른 글

| [베릴로그] EP.4 4-bit ripple carry adder의 testbench (리플캐리애더의 테스트벤치 만들기 ) (0) | 2021.01.13 |

|---|---|

| [베릴로그] EP.3 4-bit 리플캐리애더 만들기 (Ripple Carry Adder) (0) | 2021.01.13 |

| [베릴로그] EP.2 1-bit Full Adder 만들기 (0) | 2020.12.30 |

| [베릴로그] EP. 1 베릴로그 시작 (Start of Verilog) (2) | 2020.12.28 |

| EP.0 디지털 논리 설계 (0) | 2020.12.20 |